- #Lattice lse vs synplify pro how to

- #Lattice lse vs synplify pro install

- #Lattice lse vs synplify pro pro

- #Lattice lse vs synplify pro software

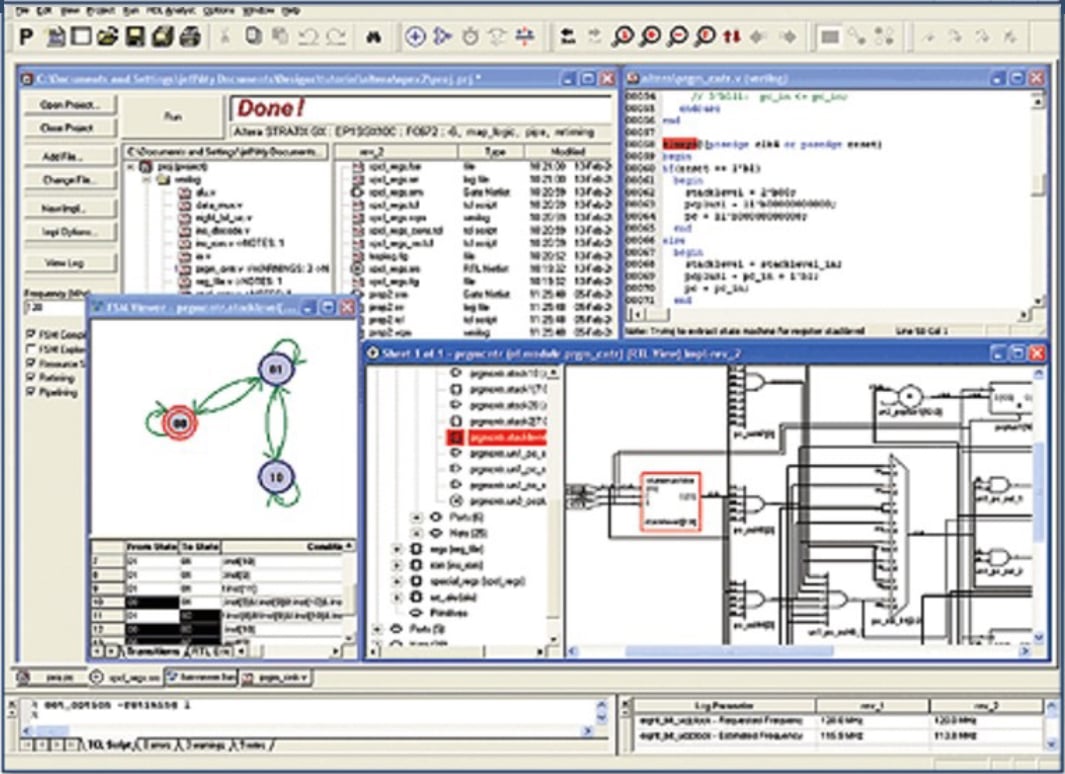

Tutorial Topics/Tools: Logic Synthesis, ispLEVER, LeonardoSpectrum.

#Lattice lse vs synplify pro how to

How to use LeonardoSpectrum to synthesize a Verilog design for a Lattice ispXPGA device. HDL Synthesis Design with LeonardoSpectrum: ispXPGA Flow Tutorial Topics/Tools: Logic Synthesis, ispLEVER, Synplify (ispLEVER 6.x) How to use Synplify to synthesize a VHDL design for a Lattice CPLD device. HDL Synthesis Design with Synplify: CPLD Flow How to use LeonardoSpectrum to synthesize a Verilog design for a Lattice CPLD device. HDL Synthesis Design with LeonardoSpectrum: CPLD Flow These symbols can be used to help with OrCAD schematic designs. xls worksheet with a list of the contents of the OLB. This file contains an OrCAD Capture Schematic Library (OLB file type) for all Lattice products. Lattice OrCAD Capture Schematic Library (OLB) PCN10A-11 Notification of Intent to Freeze ispLEVER After Version 8.2

#Lattice lse vs synplify pro software

This document explains how to use Synopsys® VCS®, Cadence® NCVerilog®, Cadence NC-VHDL®, and Aldec Riviera Pro® and Active-HDL® software to simulate designs that target Lattice Semiconductor FPGAs. Simulating Designs for Lattice FPGA Devices Includes comprehensive instructions on how to use the ispLEVER tools to design for Lattice FPGAs. Macros are compatible with ispMACH 4000 Family CPLDs. (ispLEVER 4.x, 5.x, 6.x, 7.x, 8.x)Ĭontains functional and pin descriptions of the schematic "generic" macros available in ispLEVER Classic. (ispLEVER 4.x, 5.x, 6.x, Classic)įPGA Physical Design Rule Check (DRC) Desk ReferenceĬontains descriptions of design rule check warning and error messages you may encounter when running your FPGA designs in ispLEVER's Project Navigator. Please note that a spreadsheet with built-in formulas is also available for use with TN1043, and available for download on this page.Ĭontains functional and pin descriptions of the schematic macros available in ispLEVER. zip contains the spreadsheet that is referenced in TN1043 Power Estimation in ispXPGA Devices (spreadsheet file) Generating a Schematic Symbol for OrCAD Capture Please follow installation instructions in the readme.txt file within the installation download.

#Lattice lse vs synplify pro install

You can also download the installation guide from the Documentation tab on this page and read it for more detailed instructions and options.įor Windows 10- Download and install the service packenabling Windows 10 support. Starting with the ispLEVER Classic Base Module, unzip the downloaded file, then double-click the extracted file and to start the installation procedure. STEP 2 - Install each ispLEVER Classic Module Note that the Base Module must be installed prior to the FPGA Module. This optional module adds support for ORCA FPGA and FPSC devices.

#Lattice lse vs synplify pro pro

It also includes the Lattice version of the Synplify™ Pro synthesis tool (I-2014.03LC) from Synopsys® for HDL synthesis as well as the Aldec Active-HDL Lattice Edition II simulator version 9.3. This includes the ispLEVER Project Navigator, and all the tools and device libraries you need to implement a design for any of the programmable families listed at the right. Use the Downloads tab on this page to download the software installers. IspLEVER Classic consists of the modules as listed below The ispLEVER Classic Base Module installation (which includes Synplify Synthesis module and Aldec Active-HDL Lattice Edition for simulation) and the ispLEVER Classic FPGA Module installation. Follow the three steps below to Download, Install, and License ispLEVER Classic.

0 kommentar(er)

0 kommentar(er)